新手学习Vivado XDMA (1) |

您所在的位置:网站首页 › vivado ip核使用手册 › 新手学习Vivado XDMA (1) |

新手学习Vivado XDMA (1)

|

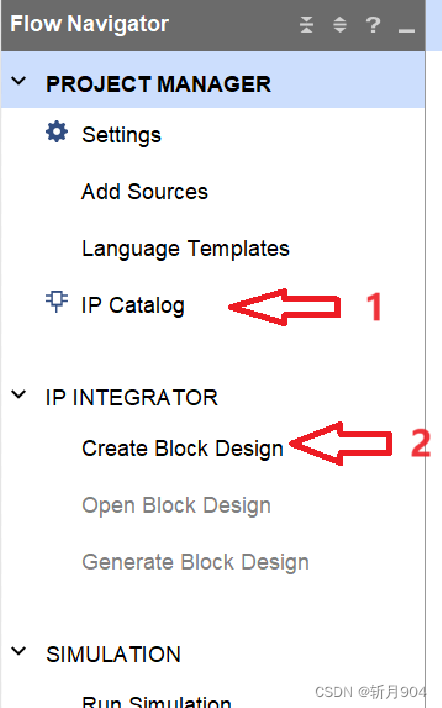

首先感谢 Xilinx XDMA 例程代码分析与仿真结果_xdma仿真-CSDN博客 的作者,也让我对XMDA有了比较多的认识,本文会从一个完全是新手的角度去理解和分析XDMA的使用,所以一旦中途有什么不懂的地方就会跳到相关的知识点进行补充说明,但因为知识浅薄,难免有理解分析出错的地方,欢迎留言反馈,共同进步。本文主要针对 XDMA (DMA/Bridge Subsystem for PCI Express) 进行了详细的配置分析,确保懂得每一个知识点,知道如何配置。 PCIe 基础知识有毅力的朋友可以先去学习下基础知识,强烈安利这个网站: PCIe扫盲系列博文连载目录篇(第一阶段)-Felix-电子技术应用-AET-中国科技核心期刊-最丰富的电子设计资源平台 (chinaaet.com)。不过笔者有时候喜欢‘急功近利“,但遇到问题就需要跳出来学习,因为有时候这样记得住一点,和问题结合下理解也深入一点。各有千秋吧。所以我们就先跳过这部分,下面就让我们开始吧。 DMA IP 生成我们使用的是 AMD 的 DMA/Bridge Subsystem for PCI Express (amd.com)。本文以Vivado 2020_2 版本为例进行说明。 首先打开 Vivado,建立一个空白工程。因为使用的是XDMA IP,并且想借用IP的example进行分析,所以可以通过以下两种途径打开,但不知为何第一种无法打开 example design,所以只能以第二种方式继续往下写。

工程名称默认即可:

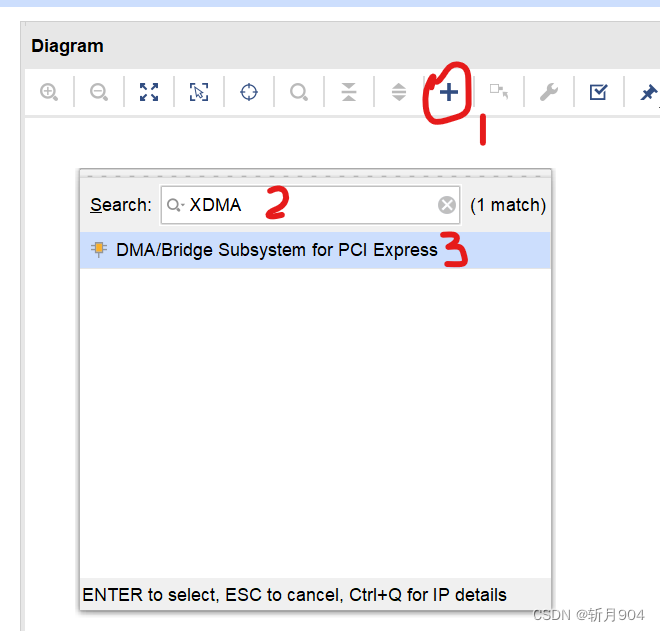

在Diagram窗口中查找DMA IP 并双击会出现的图形化模块

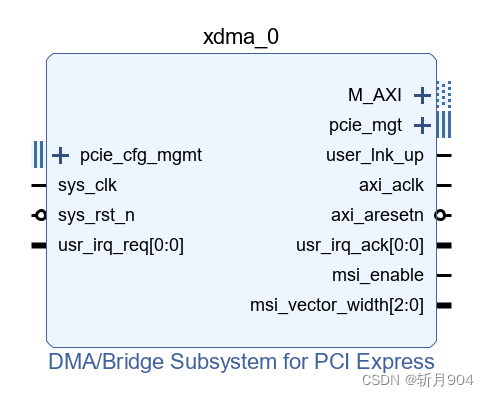

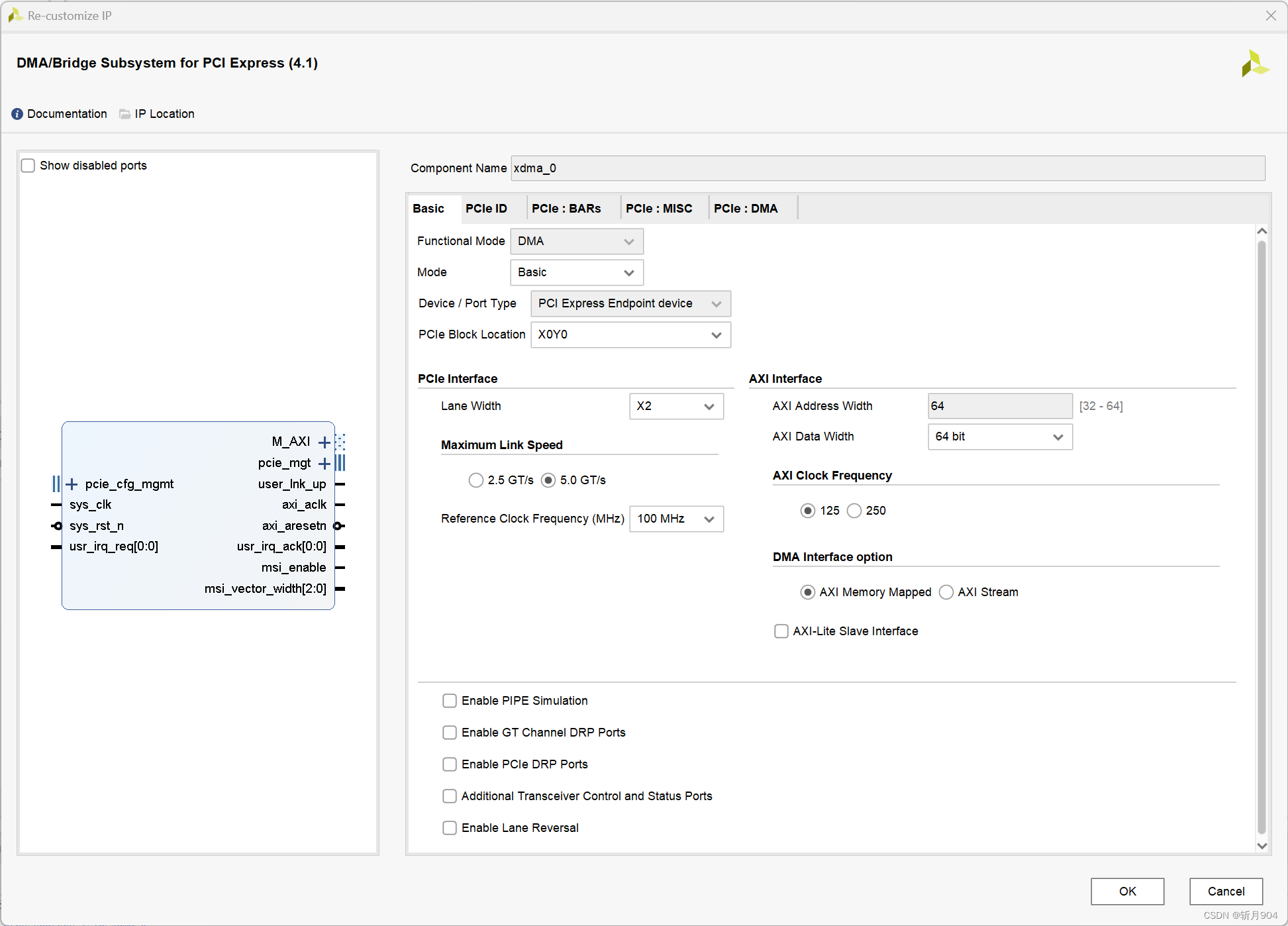

双击xdma_0模块就会出现配置界面,下面针对配置进行逐一分析。 IP 配置分析 Basic

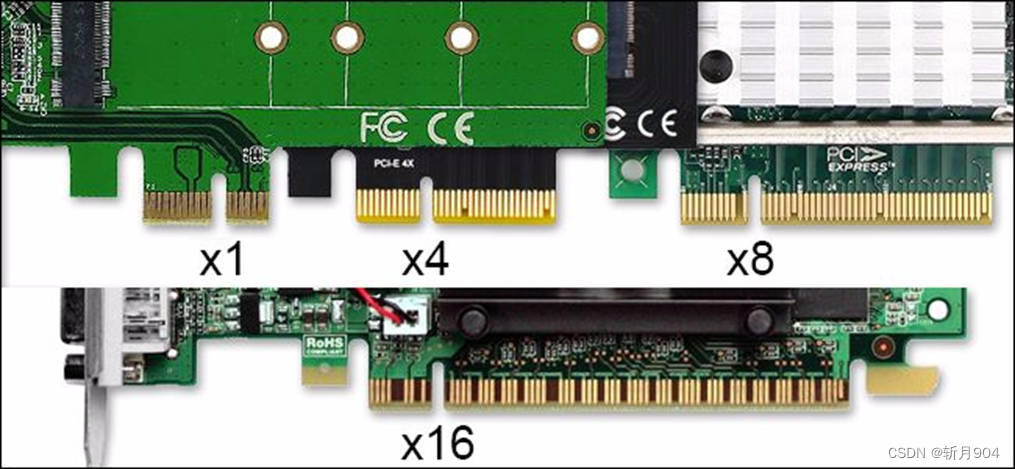

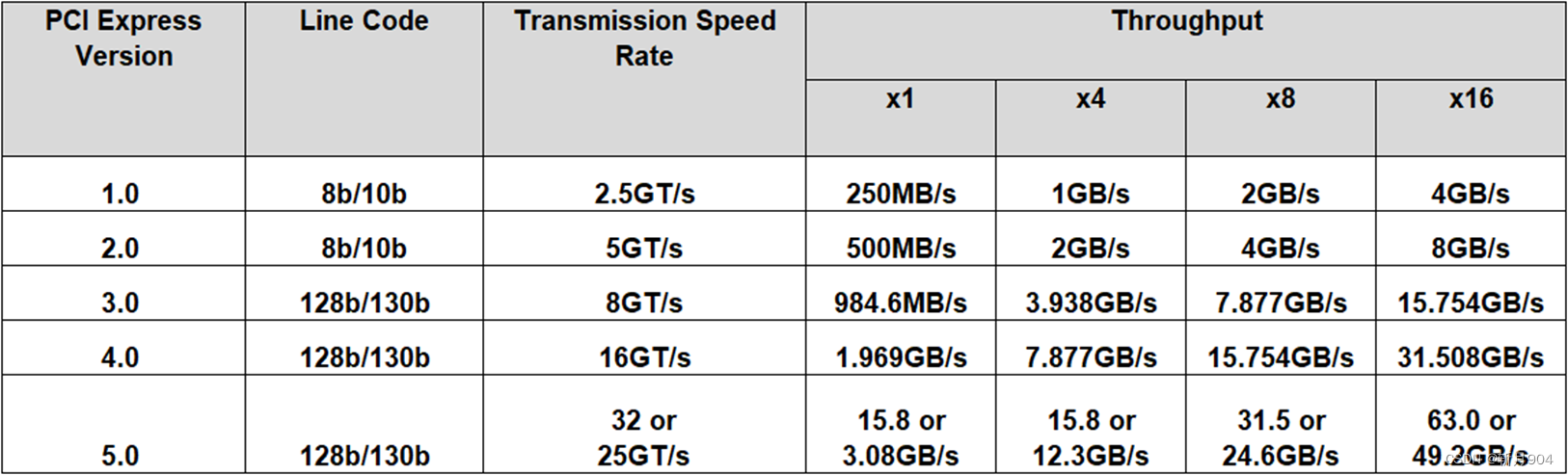

Basic 页面就是笔者选择的配置: Functional Mode: 可以看出目前 Artix 7 只支持DMA模式Mode: 选择Basic 就够用了Device: 也选择不了其他的,我们的应用是作为EP(End Point), 也就是类似显卡插在 PC 主机的 PCIe 插槽里,所以可以理解为 EP, 还有个 RP(Root Point) 概念,PC 主机(CPU)就可以称为 RP。PCIe Block Location: 对于我选择的这一款 FPGA 来说,只有一个位置可以选,规模大点的FPGA应该支持多个位置,注意 DMA 这个 IP 把 PCIe 的硬core 也包含进来了,所以这里需要我们选择 PCIe 对外的接口位置。Lane Width: 可以理解为 PCIe 数据通信的通道数量,X2 就是支持2个通道。不同的PCIe 版本不同的通道数量,最终的吞吐量也是不一样的。下图(来自网络)显示的是不同的通道数和对应的吞吐量。举个例子,笔者的PCIe 开发板是2.0接口的,那么对应的传数速率等级为 5GT/s, 可以理解为 每秒传输bit数为 5Gbps,但由于是 8b10b编码,所以是5*8/10=4Gbps=500MB/s。笔者的PCIe 接口是 x4的,但因为FPGA 的另外两个接了 SFP 光口,所以只能用x2,即 2个lanes。所以最终理论可达1GB/s。另外补充下 1个lane 就是1对 TX/RX,而每个 TX/RX 都是一对差分信号线。

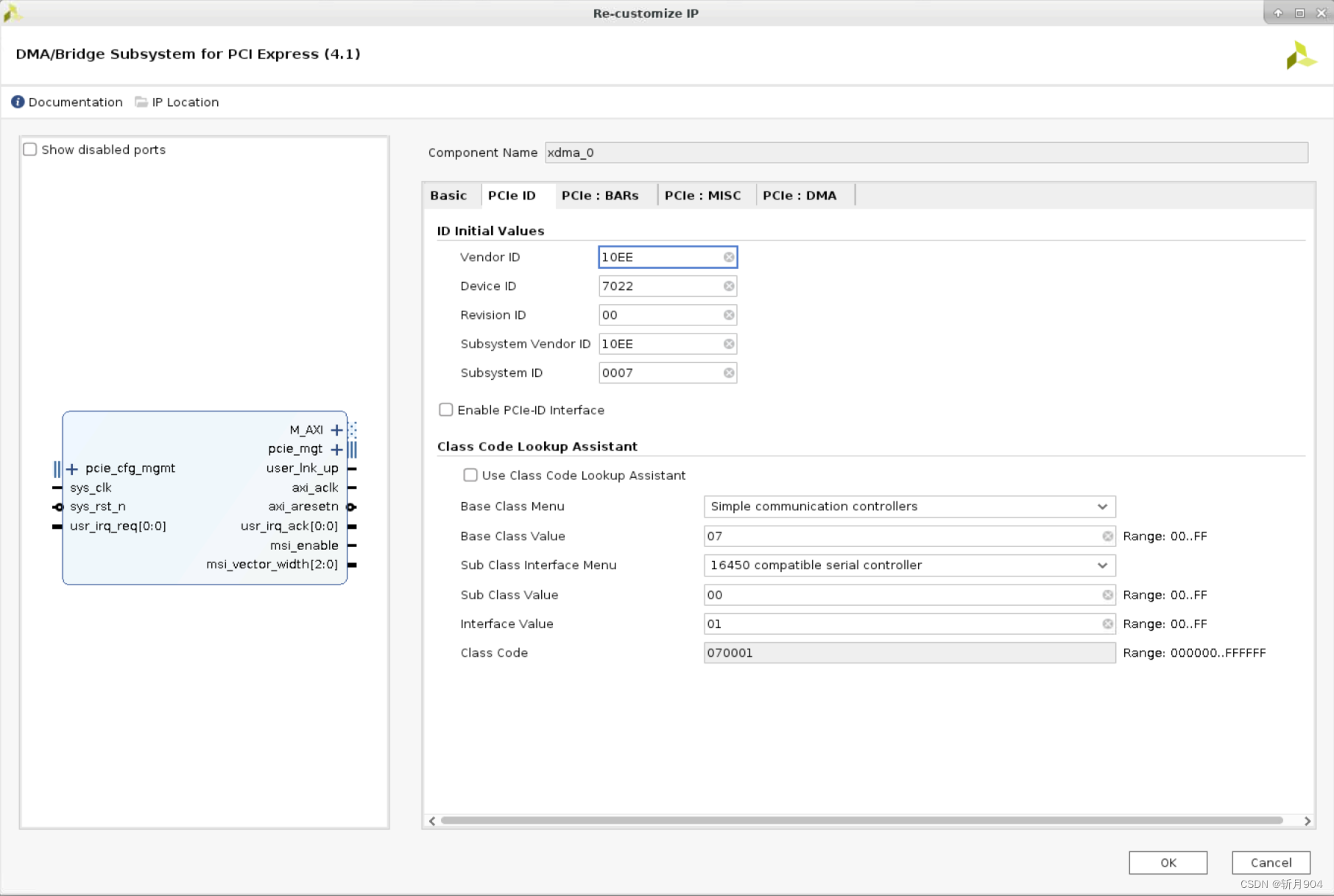

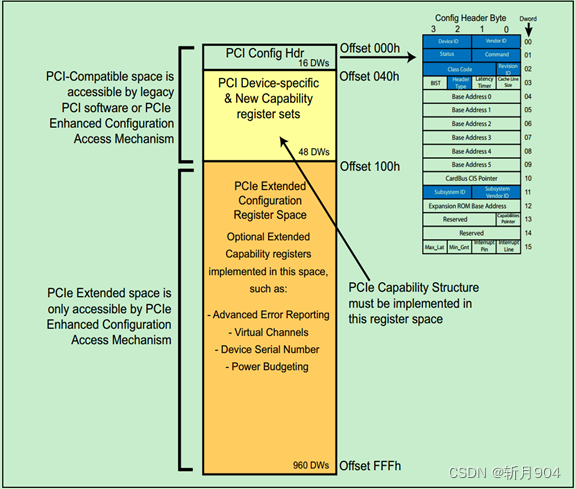

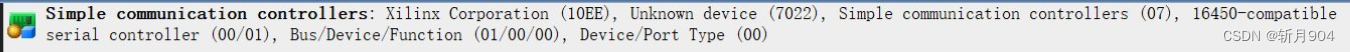

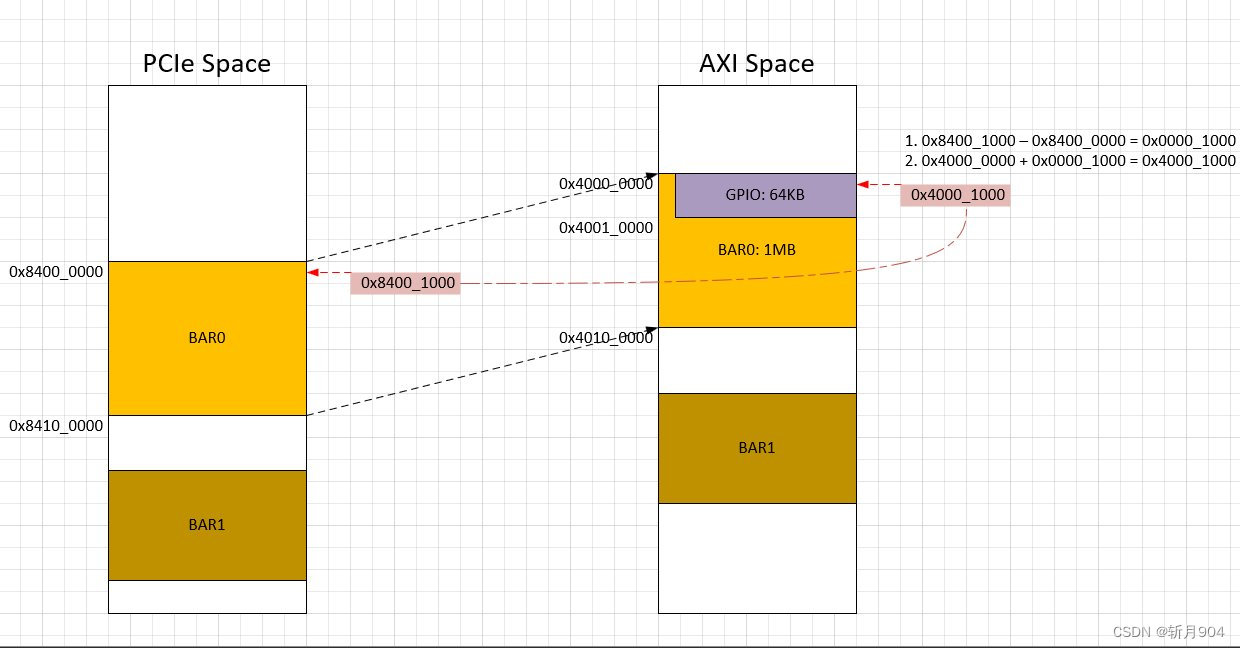

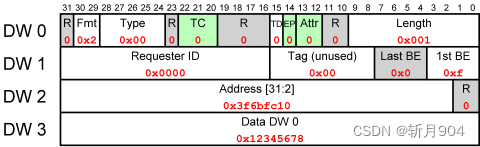

这页不需要更改配置,默认就行,但可以解释下。 ID initial Values Vendor ID: 10EE 是Xilinx 公司的设备(FPGA PCIe)的ID,由PCI Special Interest Group指定,ID唯一。Device ID: 以这里的7022为例,7表示7系列器件,如果是8和9那么代表是的 UltraScale和UltraScale+器件。0代表EP(显然,1代表RP)。第1个2表示lane的数量,即X2,注意最多的X16需要用F来表示。第2个2表示当前PCIe EP的版本,这里就是PCIe Gen2(2.x)。Revision ID: 表示器件ID的扩展,暂时不用关心Subsystem Vendor ID: 子系统供应商ID, 对于Xilinx来说,因为是同一家公司,所以这里和Vendor ID保持一致,如果不一致,可能会出现问题(看到有其他人这么分析过,笔者没有证实)。Subsystem ID: 和Device ID类似,我们选择默认即可。Enable PCIe-ID interface: 勾选以后,会有pcie_id的接口,我们不需要读取此ID,Host 通过协议可以访问到相关ID。 Class Code在开始解释说明之前,我们需要跳出来学习一个PCIe 配置空间的概念。其实,PCI有三个相互独立的物理地址空间: memory地址空间、I/O地址空间和配置空间。我们可以通过读取配置空间获得设备的信息,也可以通过配置空间来配置设备。下图显示了EP模式下配置空间的Header(64 DWs):

其中第03个DW高3个字节就是Class Code. 具体解释可以参考: PCIe配置空间(PCIE Configuration Space) – 类型码(Class Code) - 码峰编程笔记 (cfnotes.com) 笔者将一个包含此IP的bit文件烧写进开发板后,安装了 TeleScan PE 软件获取到PCIe开发板的如下信息:

从第一句话中可见系统已经成功识别了这是来自Xilinx公司的PCIe 设备。Class的配置和我们配置界面 070001 也是一致的。 PCIe : BARs

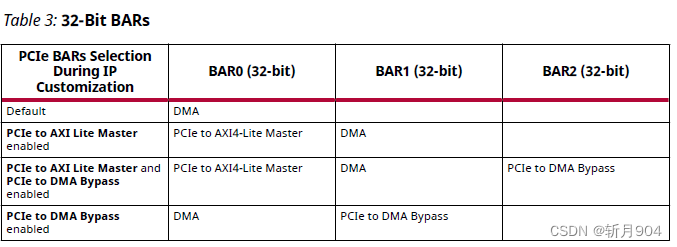

这里有3个接口可以选择,如果都勾选上了,那么根据定义分为为:BAR0,BAR1,BAR2

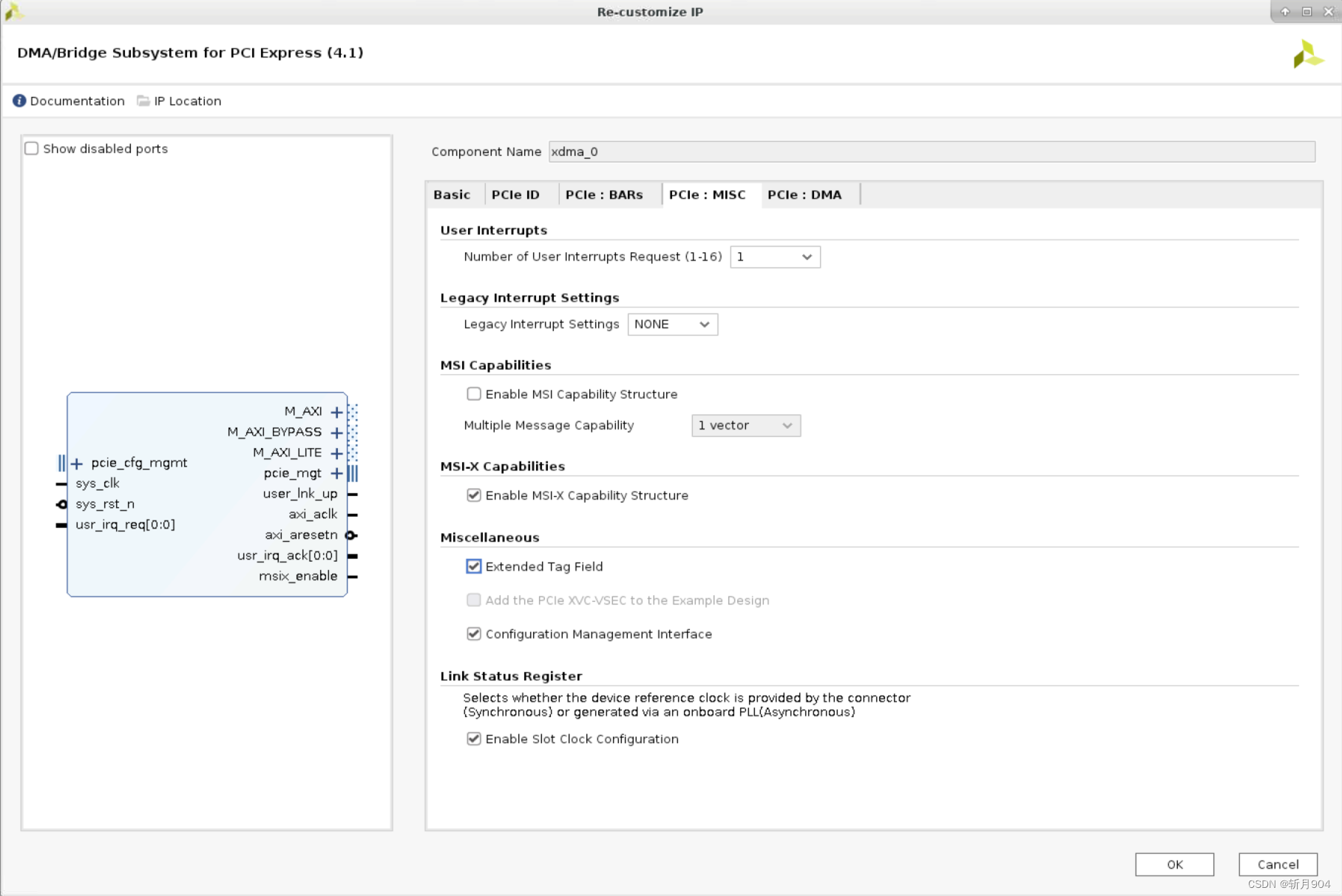

DMA空间,这里IP隐藏了一些配置,DMA需要256KB地址,这是默认设置。 BAR2和BAR0的配置理解一致。 PCIe: MISC

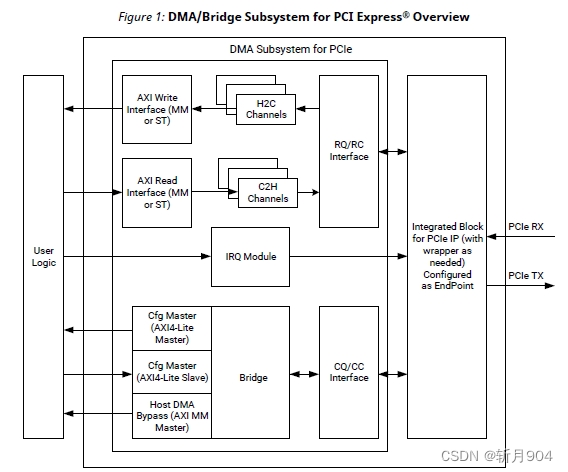

在开始解释各个配置之前,我们可以先看下整个DMA的框图,如下

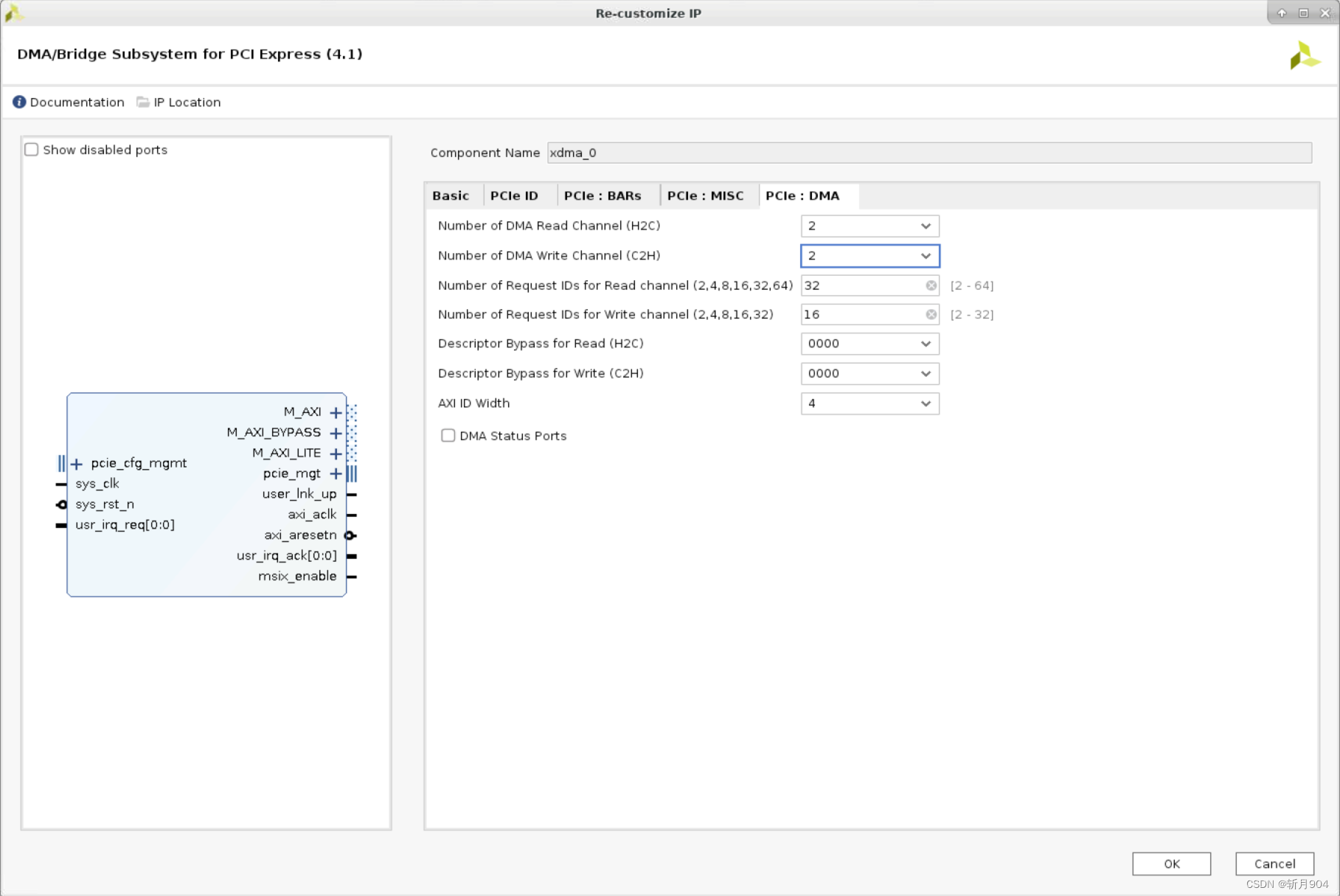

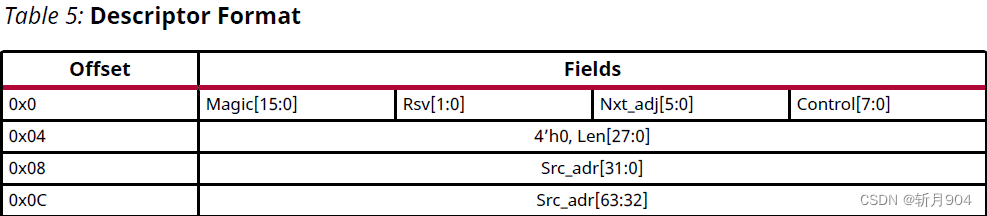

框图中上半部分中有H2C和C2H模块,并且是多个叠加的。H2C 主要表示数据的搬运方向是从右边的Host 发送到左边的Card(可以理解为PCIe卡)。 Number of DMA Read Channel(H2C):从用户侧(EP)的角度看,是向Host读数据的通道,通道数越多,一般传输速率越快。Number of DMA Write Channel(H2C):从用户侧(EP)的角度看,是向Host写数据的通道,通道数越多,一般传输速率越快。Number of Request IDs: 指的是在途(或者叫提前)发起的读写请求数量,我们选择默认就行Descripor Bypass: 描述符旁通。再跳出来复习下什么叫DMA,可以参考这里的DMA 和 LL-DMA, DMA、链式DMA、RDMA(精华讲解)_sg_alloc_table_from_pages-CSDN博客。然后这里需要解释下这个描述符的作用。描述符可以认为是一种指令,指令里面包含了数据搬运的源地址,目的地址,搬运多少等信息。对于我们当前的设计来说,我们采用的是AXI-MM接口,这意味着Host是知道用户侧的目标地址的,所以我们不能旁通这个描述符,即需要使用这个描述符中的地址信息。如果Host不知道地址,那么我们就需要旁通这个功能,并且因此会在输入接口上多出bypass的接口,由FPGA用户侧来组装这样的地址信息发送给IP。注意,每个bit对应是上面 H2C/C2H的每个通道。

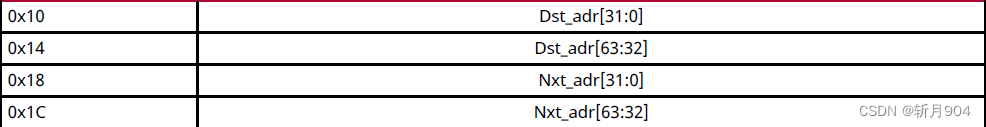

到此为此,所有的配置工作已经完成,点击完成。 打开example design后续我们可以通过右键这个IP,打开example design 进一步分析其工作机制。注意,这步操作会自动新建一个工程。

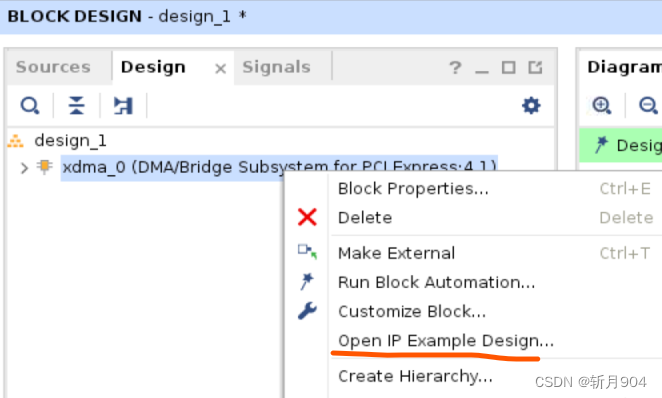

最后的结果如下,后续再更新第二章内容,关于如何认识仿真环境。

|

【本文地址】

今日新闻 |

点击排行 |

|

推荐新闻 |

图片新闻 |

|

专题文章 |